计算机组成与体系结构

软考笔记,主要记录软考考点知识,后续持续更新。

计算机结构

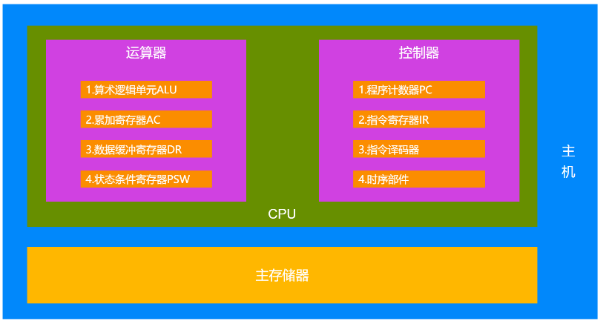

CPU 包含:运算器和控制器

- 运算器:算术逻辑单元ALU 、累加寄存器AC、数据缓冲寄存器DR、状态条件寄存器PSW;

- 算术逻辑单元(Arithmetic Logic Unit,简称ALU)它负责执行算术和逻辑操作;

- 累加寄存器(Accumulator Register,简称AC),用于存储和累加运算结果;

- 数据缓冲寄存器(Data Buffer Register,简称DR)是一种在计算机中用于暂时存储数据的寄存器;

- 状态条件寄存器(Status Condition Register,简称CCR)是一种用于保存计算机处理器运行状态的寄存器;

- 控制器:程序计数器PC、指令寄存器IR、指令译码器、时序部件;

1. 程序计数器(Program Counter,PC)是一种寄存器,用于存储CPU当前执行的指令的内存地址。它在CPU执行指令时不断更新,指向下一条要执行的指令的内存地址; CPU首先从程序计数器(PC)获得需要执行的指令地址,从内存(或高速缓存)读取到的指令则暂存在指令寄存器(IR),然后进行分析和执行;

2. 指令寄存器(Instruction Register,IR)是一种寄存器,用于存储当前CPU正在执行的指令,当程序计数器PC指向下一条指令的内存地址时,指令寄存器IR会将该指令从内存中取出并保存在其中,以便CPU能够解码和执行该指令;

3. 指令译码器(Instruction Decoder)是CPU中的一种模块,负责解析指令寄存器IR中存储的二进制指令,并将其转换为CPU能够理解和执行的控制信号,用于将不同的指令编码映射到相应的操作控制信号;

4. 时序部件(Timing Control Unit)是CPU中的一个模块,负责控制和调节CPU内部各个组成部分之间的时序关系。它通常包括计时器、时钟发生器等模块,可以确保指令和数据在正确的时间被读取和写入寄存器、缓存和内存中,以及确保各个部件之间协同工作的顺序和时间关系符合CPU设计要求;

计算机体系结构分类 Flynn

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个处理器 :一个主存模块:一个 | 单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个处理器 :多个主存模块:多个 | 各处理器以异步的形式执行同一条指令 | 并行处理器阵列处理器超级向量处理器 |

| 多指令流单数据流MISD | 控制部分:多个处理器 :一个主存模块:多个 | 被证明不可能,至少是不实际 | 目前没有,有文献称流水线计算器为此类 |

| 多指令流多数据流MIMD | 控制部分:多个处理器 :多个主存模块:多个 | 能够实现作业、任务、指令等各级全面并行 | 多处理机系统多计算机 |

CISC 与 RISC

- CISC代表复杂指令集计算机(Complex Instruction Set Computer),是一种计算机处理器架构的类型,其指令集非常丰富和复杂。CISC处理器通常具有高度优化的指令集,这些指令可以在单个指令中执行多个低级操作,从而提高了处理器的效率和性能。然而,由于指令集的复杂性,CISC处理器的设计和实现成本较高,且难以实现高性能的并行处理;

- RISC代表精简指令集计算机(Reduced Instruction Set Computer),是一种计算机处理器架构的类型,其指令集相对较少和简单。RISC处理器通常执行基本指令,每个指令只执行一个低级操作,并使用流水线技术来实现高性能并行处理。由于其指令集简单,RISC处理器的设计和实现成本相对较低,且易于实现高性能的并行处理。近年来,大多数计算机处理器都采用了RISC设计,例如ARM和PowerPC;

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其它 |

|---|---|---|---|---|

| CISC(复杂) | 数量多,使用频率差别大,可变长格式 | 支持多种 | 微程序控制技术(微码) | 研制周期长 |

| RISC(精简) | 数量少,使用频率接近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存 | 支持方式少 | 增加了通用寄存器:硬布线逻辑控制为主;适合采用流水线 | 优化编译,有效支持高级语言 |

流水线

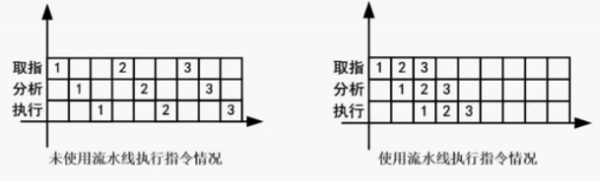

流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理时针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度。

坐标中格子数字,表示正在执行的指令

大致流程为:-》取指-》分析-》执行-》

这种方式现实中运用很广泛,举一个有点奇怪的例子吧,种树。

我们假设有三个人做这个事情,甲:运树;乙:栽树;丙:浇水,交完水代表这件事情做了一次。

未使用流水线执行任务情况为:甲把树运过来(运树期间乙丙只能休息)=》乙栽树(栽树期间甲丙只能休息)=》丙浇水(缴税期间甲乙只能休息)。如此循环,总有两个人处于休息的状态。

使用流水线执行任务情况为:甲负责不停的把树一颗一颗运过来,乙负责不停地把数一颗一颗的栽上去,丙负责不停地一颗一颗教书。这样三个人同时在工作,没有休息的时刻,效率最高。类似工厂的流水线也是这样。

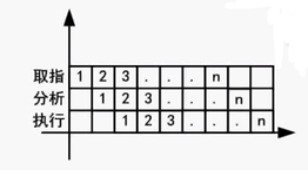

流水线计算

流水线周期为执行时间最长的一段

流水线的计算公式为:

1条指令执行时间 + (指令条数-1) * 流水线周期

- 理论公式:$(t1+t2+ \cdot \cdot \cdot +tk)+(n-1) \times△t$

- 实践公式:$(k+n-1) \times△t$

注:t1,t2,……tk表示一条指令每一段执行的时间(如上图取指时间,分析时间,执行时间);n表示执行了多少条指令;$△t$表示流水线周期时间(即指令执行时间最长的一段);k表示该条指令执行分成了几段

例题

若指令流水线把一条指令分为取指、分析和执行三部分,且三部分的时间分别是取指2ns=》分析2ns=》执行1ns。那么,流水线周期是多少?100条指令全部执行完毕需要的时间是多少?

分析:流水线周期为执行时间最长的一段,故该题中流水线周期为2ns;100条指令全部执行完毕我们直接套用公式:(第一条指令取指时间+第一条指令分析时间+第一条指令执行时间)+99条指令*周期时间。即:(2+2+1)+(100-1)*2=203,即为100条指令全部执行完毕需要的理论时间。

按照实践公式计算:任务执行分为了3段,取指、分析、执行。所以(3+100-1)*2=204ns

流水线吞吐率计算

流水线的吞吐率(Thougn put rate, TP)是指在单位时间内流水线所完成的任务数量或输出的结果数量。计算流水线吞吐率的最基本的公式如下:

$TP = \frac{指令条数}{流水线执行时间}$

以上题为例,执行100条指令流水线执行时间为203,那么吞吐率即为:$TP= \frac{100}{203}$

流水线最大吞吐率

$TP_{max} = \lim\limits_ { n \rightarrow + \infty } \frac{n}{(k+n-1)△t}= \frac{1}{△t}$

以上题为例,执行1条指令的周期时间为2ns,那么流水线最大吞吐量为:

$TP_{max}= \frac{1}{△t}=\frac{1}{2}$

流水线的加速比

完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比称为流水线的加速比。计算流水线加速比的基本公式如下:

$S = \frac{不使用流水线执行时间}{使用流水线执行时间}$

还以上述为例:执行一条指令所用的时间为:2ns取指;2ns分析;1ns执行。

不使用流水线完成100条指令所消耗的时间为:(2+2+1)*100 = 500ns

使用流水线完成100条指令所消耗的时间为:(2+2+1)+(100-1)*2=203ns

所以流水线的加速比为:$S = \frac{500}{203}$

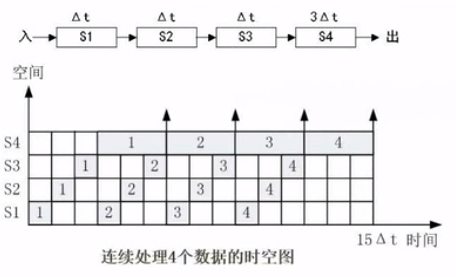

流水线的效率

流水线的效率是指流水线的设备利用率。在时空图上,流水线的效率定义为n个任务占用的时空区与k个流水段总的时空区之比。

计算流水线效率的公式为:$E = \frac{n个任务占用的时空区}{k个流水段的总的时空区}=\frac{ T_{0} }{kT_{k}}$

例题

求出图中流水线效率。

分析:

处理一个数据所需要△t+△t+△t+3△t,处理4个数据即为:(△t+△t+△t+3△t)*4。即计算所有有色方块所占用的空间数

如图可知我们横向需要15个△t,每个△t分为4段,即总数为15△t*4。即计算所有方块所占用的空间数

所以体重的流水线效率为:$E= \frac{(△t+△t+△t+3△t) \times 4}{15△t \times 4}=\frac{24△t}{60△t}$

Cache

● Cache的功能:提高CPU数据输入输出的速率,突破冯·诺依曼瓶颈,即CPU与存储系统间数据传送带宽限制。

● 在计算机的存储系统体系中,Cache是访问速度最快的层次。

● 使用Cache改善系统性能的依据是程序的局部性原理。

如果以h代表Cache的访问命中率,

其中,(1-h)又称为失效率(未命中率)

用能听懂的话来讲:假如

50.95ns使一个只使用主存存储器读取速度有了巨大的提升

主存-编址

按字存址:存储体的存储单元是字存储单元,即最小寻址单位是字

按字节存址: 存储体的存储单元是字节存储单元,即最小寻址单位是字节

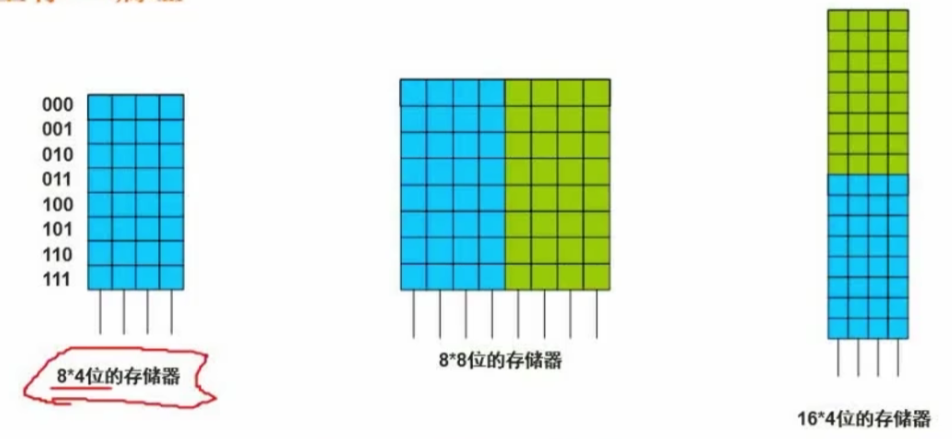

根据存储器所要求的容量和选定的存储芯片的容量 就可以计算出所需芯片的总数,即:

总片数=总容量/每片的容量

例题1

存储地址区间为 4000H~43FFH,每个存储单元可存16位二进制数 该内存区域用四片存储器芯片构成,则构成该内存存储芯片的容量是多少?

首先算出总容量: 43FFH-4000H +1

之所以+1 是因为这算的是单元的数量 例如 4~2 之间算出来 它只有二个单元,但实际上 4 3 2 一共有三个单元 所以最后得加+1 ,

总容量:400H(转2进制) :100 0000 0000(转十进制)1024

总片数:4

又因为每个存储单元存储16位二进制

每片的容量= 16*1024/4

例题2

内存地址从AC000H到C7FFFH,共有 (1) K个地址单元,如果该内存地址按字(16bit)编址,由28片存储器芯片构成。已知构成此内存的芯片每片有16K个存储单元,则该芯片每个存储单元存储 (2) 位。

解析:

(H不参与计算只是标识)

首先还是计算出AC000H到C7FFFH之间的总容量:C7FFF-AC000+1

16进制A即10;C即12;F即15,所以总容量 = C7FFF-AC000+1 = 1BFFF +1 = 1C000H

16进制换算为10进制1C000=>116*$1 \times16^{4}+12 \times16^{3}+0 \times16^{2}+0 \times16^{1}+0 \times16^{0} = 114688$

(1)中要填写的多少K,字节换算成千字节K需要除以1024即:114688/1024 = 112,所以(1)答案为112

芯片每个存储单元存储位 X 等于$(112K \times 16) = 28 \times 16k \times X$ 得出 X = 4;